Question

a.

Internal interrupts

b.

External interrupts

c.

Software interrupts

d.

None of the above

Engage with the Community - Add Your Comment

Confused About the Answer? Ask for Details Here.

Know the Explanation? Add it Here.

Q. For switching from a CPU user mode to the supervisor mode following type of interrupt is most appropriate

Similar Questions

Discover Related MCQs

Q. In a dot matrix printer the time to print a character is 6 m:sec., time to space in between characters is 2 m.sec., and the number of characters ina line are 200. The printing speed of the dot matrix printer in characters per second and the time to print a character line are given by which of the following options?

View solution

Q. Match the following 8085 instructions with the flags:

a. XCHG i. only carry flag is affected.

b. SUB ii. no flags are affected.

c. STC iii. all flags other than carry flag are affected.

d. DCR iv. all flags are affected.

code:

a b c d

View solution

Q. How many times will the following loop be executed?

LXI B, 0007 H

LOP: DCX B

MOV A,B

ORA C

JNZ LOP

View solution

Q. Specify the contents of the accumulator and the status of the S, Z and CY flags when 8085 microprocessor performs addition of 87 H and 79 H.

View solution

Q. Which of the following statements is not true?

View solution

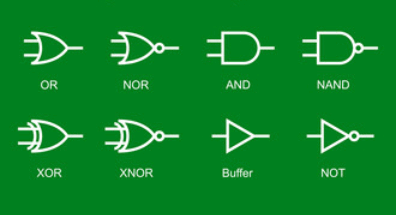

Q. Consider the following statements :

(a) Boolean expressions and logic networks correspond to labelled acyclic digraphs.

(b) Optimal Boolean expressions may not correspond to simplest networks.

(c) Choosing essential blocks first in a Karnaugh map and then greedily choosing the largest remaining blocks to cover may not give an optimal expression.

Which of these statement(s) is/ are correct

View solution

Q. Consider a full adder with the following input values :

(a) x=1, y=0 and Ci(carry input) = 0

(b) x=0, y=1 and Ci = 1

Compute the values of S(sum) and C0 (carry output) for the above input values.

View solution

Q. In the case of parallelization, Amdahl's law states that if P is the proportion of the program that can be made parallel and (1 - P) is the proportion that cannot be parallelized , then the maximum speed that can be achieved by using N processors is

View solution

Q. Which of the following statements is incorrect for Parallel Virtual Machine (PVM)?

View solution

Q. Which of the following is not valid with reference to Message Passing Interface (MPI) ?

View solution

Q. For the 8 - bit word 00111001, the check bits stored with it would be 0111. Suppose when the word is read from memory, the check bits are calculated to be 1101. What is the data word that was read from memory?

View solution

Q. Consider a 32 - bit microprocessor, with a 16 - bit external data bus, driven by an 8 MHz input clock. Assume that this microprocessor has a bus cycle whose minimum duration equals four input clock cycles. What is the maximum data transfer rate for this microprocessor?

View solution

Q. The RST 7 instruction in 8085 microprocessor is equivalent to :

View solution

Q. The CPU of a system having 1 MIPS execution rate needs 4 machine cycles on an average for executing an instruction. The fifty percent of the cycles use memory bus. A memory read/ write employs one machine cycle. For execution of the programs, the system utilizes 90 percent of the CPU time. For block data transfer, an IO device is attached to the system while CPU executes the background programs continuously. What is the maximum IO data transfer rate if programmed IO data transfer technique is used?

View solution

Q. The number of flip-flops required to design a modulo - 272 counter is :

View solution

Q. Consider a uniprocessor system where new processes arrive at an average of five processes per minute and each process needs an average of 6 seconds of service time. What will be the CPU utilization ?

View solution

Q. The advantage of _______ is that it can reference memory without paying the price of having a full memory address in the instruction.

View solution

Q. The output of a sequential circuit depends on

View solution

Q. Which of the following flip-flops is free from race condition ?

View solution

Q. Pipelining improves performance by:

View solution

Suggested Topics

Are you eager to expand your knowledge beyond Computer Architecture? We've curated a selection of related categories that you might find intriguing.

Click on the categories below to discover a wealth of MCQs and enrich your understanding of Computer Science. Happy exploring!