Question

a.

rotating priority scheme

b.

fixed priority scheme

c.

rotating priority and fixed priority scheme

d.

none of the mentioned

Posted under Microprocessor

Engage with the Community - Add Your Comment

Confused About the Answer? Ask for Details Here.

Know the Explanation? Add it Here.

Q. The priority of the channels varies frequently in

Similar Questions

Discover Related MCQs

Q. The register of 8257 that can only be written in is

View solution

Q. The operation that can be performed on the status register is

View solution

Q. In DMA the data transfer is controlled by

View solution

Q. Cycle stealing technique is used in

View solution

Q. During DMA acknowledgement cycle, CPU relinquishes

View solution

Q. Access time is faster for _________.

View solution

Q. DMA stands for

View solution

Q. If the crystal oscillator is operating at 15 MHz, the PCLK output of 8284 is

View solution

Q. In which T-state does the CPU sends the address to memory or I/O and the ALE signal

for demultiplexing

View solution

Q. If a 1M ×1 DRAM requires 4 ms for a refresh and has 256 rows to be refreshed, no

more than __________ of time must pass before another row is refreshed.

View solution

Q. In a DMA write operation the data is transferred

View solution

Q. Which type of JMP instruction assembles if the distance is 0020 h bytes

View solution

Q. A certain SRAM has CS = 0 , WE = 0 and OE = 1. In which of the following

modes this SRAM is operating

View solution

Q. Which of the following is true with respect to EEPROM?

View solution

Q. Which microprocessor pins are used to request and acknowledge a DMA transfer?

View solution

Q. Software command CLEAR MASK REGISTER in DMA

View solution

Q. The common register(s) for all the four channels of 8257 is

View solution

Q. The IOW (active low) in its slave mode loads the contents of a data bus to

View solution

Q. To indicate the I/O device that its request for the DMA transfer has been honored by the CPU, the DMA controller pulls

View solution

Q. The number of clock cycles required for an 8257 to complete a transfer is

View solution

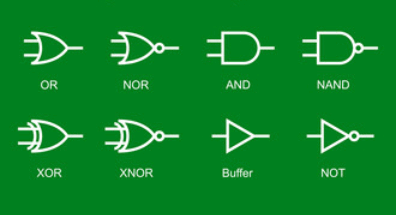

Suggested Topics

Are you eager to expand your knowledge beyond Microprocessor? We've curated a selection of related categories that you might find intriguing.

Click on the categories below to discover a wealth of MCQs and enrich your understanding of Computer Science. Happy exploring!

.png)