Question

a.

Active-Medium

b.

Active-Low

c.

Active-High

d.

Both b and c

Posted under Computer Architecture

Engage with the Community - Add Your Comment

Confused About the Answer? Ask for Details Here.

Know the Explanation? Add it Here.

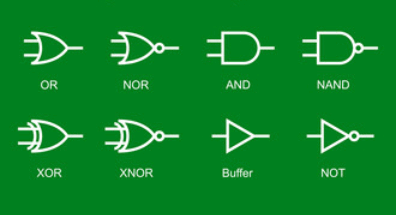

Q. Asynchronous inputs, just like synchronous inputs, can be engineered to be ______________.

Similar Questions

Discover Related MCQs

Q. ___________ and Clear should not be 0 at the same time; otherwise, both the outputs will be 1, which is known as invalid state.

View solution

Q. Which table indicates the input conditions of the flip-flops necessary to cause all possible next state transitions of a flip-flop?

View solution

Q. When a circuit is self- correcting?

View solution

Q. A PLA consists of two-level____________ circuits on a single chip.

View solution

Q. In which of the following types of counters, the flip-flops do not change states at exactly the same time?

View solution

Q. The number of states through which the counter goes is also known as ____________.

View solution

Q. It contains an equal resistor or current source segment for each possible value of DAC output.

View solution

Q. The total current can be converted into the corresponding voltage by using a/an _______________.

View solution

Q. The number of resistors required for an N-bit DAC is 2N in the case of _____________.

View solution

Q. The characteristics of a DAC, which are generally specified by the manufacturers

View solution

Q. To start the conversion in successive approximation DAC the programmer sets the MSB to ___________ and all other bits to __________.

View solution

Q. The major block(s) of the dual- slope ADC

View solution

Q. A counter with 10 states

View solution

Q. In asynchronous flip-flop, ______________ and clear pin shows negation.

View solution

Q. It is a single input version of J-K flip-flop formed by tying both the inputs of J-K.

View solution

Q. In flip-flop, the ___________ arrow shows positive transition on the clock.

View solution

Q. Gated S-R latch is a combination of which latch and gate?

View solution

Q. Which of the following is the advantage of PLD over ICs?

View solution

Q. In a DAC, the possible number of digital input is __________.

View solution

Q. An n-bit register has a group of n flip-flops and some

View solution

Suggested Topics

Are you eager to expand your knowledge beyond Computer Architecture? We've curated a selection of related categories that you might find intriguing.

Click on the categories below to discover a wealth of MCQs and enrich your understanding of Computer Science. Happy exploring!