Question

a.

4

b.

8

c.

16

d.

32

Engage with the Community - Add Your Comment

Confused About the Answer? Ask for Details Here.

Know the Explanation? Add it Here.

Q. In 8085 microprocessor the address bus is of .................... bits.

Similar Questions

Discover Related MCQs

Q. In which addressing mode, the effective address of the operand is generated by adding a constant value to the contents of register ?

View solution

Q. The efficiency (E) and speed up (sp) for Multiprocessor with p processors satisfies

View solution

Q. In an enhancement of a CPU design, the speed of a floating point unit has been increased by 20% and the speed of a fixed point unit has been increased by 10%. What is the overall speed achieved if the ratio of the number of floating point operations to the number of fixed point operations is 2 : 3 and the floating point operation used to take twice the time taken by the fixed point operation in original design ?

View solution

Q. Suppose a processor does not have any stack pointer registers, which of the following statements is true ?

View solution

Q. Let f be the fraction of a computation (in terms of time) that is parallelizable, P the number of processors in the system, and sp the speed up achievable in comparison with sequential execution – then the sp can be calculated using the relation :

View solution

Q. FAN IN of a component A is defined as

View solution

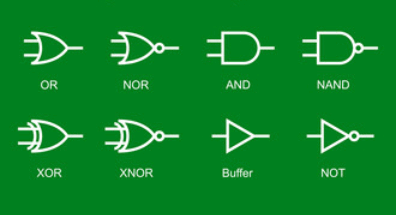

Q. Which of the following statements are true?

I. A circuit that adds two bits, producing a sum bit and a carry bit is called half adder.

II. A circuit that adds two bits, producing a sum bit and a carry bit is called full adder.

III. A circuit that adds two bits and a carry bit producing a sum bit and a carry bit is called full adder.

IV. A device that accepts the value of a Boolean variable as input and produces its complement is called an inverter.

View solution

Q. Match the following:

List -I List - II

a. Indexed i. is not used when an

Addressing operand is moved from memory into a register' or from a register to memory.

b. Direct ii.Memory address is computed by adding up two registers plus an (optional) offset.

Addressing

c. Register iii.Addressing memory by giving a register plus a content offset.

Addressing

d. Base- iv .can only be used to access global variables whose address 18 known at compile time. Indexed

Addressing

View solution

Q. Which of the following is a design criteria for instruction formats ?

View solution

Q. Synchronization is achieved by a __________timing device which generates a periodic train of ____________

View solution

Q. Serial access memories are useful in applications where

View solution

Q. The essential difference between traps and interrupts is

View solution

Q. The size of the ROM required to build an 8-bit adder/subtractor with mode control, carry input, carry output and two's complement overflow output is given as

View solution

Q. A specific editor has 200 K of program text, 15 K of initial stack, 50 K of initialized data, and 70 K of bootstrap code. If five editors are started simultaneously, how much physical memory is needed if shared text is used?

View solution

Q. A hierarchical memory system that uses cache memory has cache access time of 50 nano seconds, main memory access time of 300 nano seconds, 75% of memory requests are for read, hit ratio of 0.8 for read access and the write-through scheme is used. What will be the average access time of the system both for read and write requests ?

View solution

Q. For switching from a CPU user mode to the supervisor mode following type of interrupt is most appropriate

View solution

Q. In a dot matrix printer the time to print a character is 6 m:sec., time to space in between characters is 2 m.sec., and the number of characters ina line are 200. The printing speed of the dot matrix printer in characters per second and the time to print a character line are given by which of the following options?

View solution

Q. Match the following 8085 instructions with the flags:

a. XCHG i. only carry flag is affected.

b. SUB ii. no flags are affected.

c. STC iii. all flags other than carry flag are affected.

d. DCR iv. all flags are affected.

code:

a b c d

View solution

Q. How many times will the following loop be executed?

LXI B, 0007 H

LOP: DCX B

MOV A,B

ORA C

JNZ LOP

View solution

Q. Specify the contents of the accumulator and the status of the S, Z and CY flags when 8085 microprocessor performs addition of 87 H and 79 H.

View solution

Suggested Topics

Are you eager to expand your knowledge beyond Computer Architecture? We've curated a selection of related categories that you might find intriguing.

Click on the categories below to discover a wealth of MCQs and enrich your understanding of Computer Science. Happy exploring!

.png)